# MX368033A CDMA2000 1xEV-DO Signal Generation Software Operation Manual (For MU368030A)

### **Second Edition**

Read this manual before using the equipment. To ensure that the equipment is used safely, read the "For Safety" in the MG3681A Digital Modulation Generator Operation Manual first. Keep this manual with the equipment.

# **ANRITSU CORPORATION**

MX368033A CDMA 2000 1xEV-DO Signal Generation Software Operation Manual (For MU368030A)

5 June 2002 (First Edition)

29 August 2003 (Second Edition)

Copyright © 2002-2003, ANRITSU CORPORATION.

All rights reserved. No part of this manual may be reproduced without the prior written permission of the publisher.

The contents of this manual may be changed without prior notice. Printed in Japan

# **Equipment Certificate**

Anritsu guarantees that this equipment was inspected at shipment and meets the published specifications.

### **Anritsu Warranty**

- During the warranty period, Anritsu will repair or exchange this software free-of-charge at the company's own discretion if it proves defective when used as described in the operation manual.

- The warranty period is 1 year from the purchase date.

- The warranty period after repair or exchange will remain 1 year from the original purchase date, or 30 days from the date of repair or exchange, depending on whichever is longer.

- This warranty does not cover damage to this software caused by Acts of God, natural disasters, and misuse or mishandling by the customer.

In addition, this warranty is valid only for the original equipment purchaser. It is not transferable if the equipment is resold.

Anritsu Corporation will not accept liability for equipment faults due to unforeseen and unusual circumstances, nor for faults due to mishandling by the customer.

# **Anritsu Corporation Contact**

If this equipment develops a fault, contact Anritsu Corporation or its representatives at the address in this manual.

### Notes On Export Management

This product and its manuals may require an Export License/Approval by the Government of the product's country of origin for re-export from your country.

Before re-exporting the product or manuals, please contact us to confirm whether they are export-controlled items or not.

When you dispose of export-controlled items, the products/manuals are needed to be broken/shredded so as not to be unlawfully used for military purpose.

### Trademark and Registered Trademark

Windows is a registered trademark of Microsoft Corporation in the United States and/or other countries.

Compact Flash <sup>™</sup> is a registered trademark of San Disk Corporation.

# **Software License Agreement**

Please read this Software License Agreement before using the accompanying software program (hereafter this software).

You are authorized to use this software only if you agree to all the terms of this License.

By opening the sealed package containing this software, you are agreeing to be bound by the terms of this License.

If you do not agree to these terms, return the unopened software package to Anritsu Corporation (hereafter Anritsu).

#### 1. License

- (1) This License gives you the right to use this software on one MG3681A (hereafter computer system).

- (2) To use this software on one computer system, this License allows you to make one copy of this software on the storage device of your computer system.

- (3) You must obtain a site license to use this software on more than one computer system even if such computer systems are not operating simultaneously.

### 2. Copyright

- (1) Although you are licensed to use this software, Anritsu retains the copyright.

- (2) Although you have purchased this software, rights other than those specified in this License are not transferred to you.

- (3) You may not print, copy, modify, create derivative works, incorporate in other software programs, decompile or disassemble this software in whole or in part, without obtaining prior written permission from Anritsu.

### 3. Copying

Notwithstanding item (3) of section 2 above, you may make one copy of this software for backup purposes only. In this case, you may only use either the backup copy or the original copy of this software.

#### 4. Termination

- Anritsu will deem this License to be automatically terminated if you fail to comply with any provision of this License. Upon termination, you will lose all rights to this software.

- (2) Either party (Anritsu or yourself) to this Software License Agreement may terminate this Agreement by giving 1 months notice in writing to the other party.

- (3) Upon termination of this License for any reason, you must either immediately destroy this software and related documentation, or return it to Anritsu.

# **CE Conformity marking**

Anritsu affixes the CE Conformity Marking on the following product (s) in accordance with the Council Directive 93/68/EEC to indicate that they conform with the EMC and LVD directive of the European Union (EU).

### **CE Marking**

# ( (

### 1. Product Model

Software:

MX368033A CDMA2000 1xEV-DO Signal Generation Software

### 2. Applied Directive and Standards

When the MU368030A universal modulation unit is installed in the MG3681A, the applied directive and standards of this unit is conformed to those of the MG3681A main frame.

PS: About main frame

The kind of main frame (a measuring apparatus) will be to increase. Please, contact us about the newest information of the main frame.

# **C-tick Conformity marking**

Anritsu affixes the C-tick marking on the following product (s) in accordance with the regulation to indicate that they conform with the EMC framework of Australia/New Zealand.

### **C-tick marking**

### 1. Product Model

Software:

MX368033A CDMA2000 1xEV-DO Signal Generation Software

### 2. Applied Directive and Standards

When the MU368030A universal modulation unit is installed in the MG3681A, the applied directive and standards of this unit is conformed to those of the MG3681A main frame.

PS: About main frame

The kind of main frame (a measuring apparatus) will be to increase. Please, contact us about the newest information of the main frame.

# **About This Manual**

This Operation Manual explains the outline, measurement examples, remote control and other aspects of MX368033A CDMA 2000 1xEV-DO Signal Generation Software. This software is designed to be installed in the MU368030A Universal Modulation Unit mounted on the MG3681A Digital Modulation Signal Generator.

represents a panel key.

The MG3681A Digital Modulation Signal Generator Operation Manual and the MU368030A Universal Modulation Unit Operation Manual are available as separate volumes.

Use them in conjunction with this Operation Manual.

# **Table of Contents**

| Abou  | It This Manual                             | I         |

|-------|--------------------------------------------|-----------|

| Secti | on 1 Overview                              | 1-1       |

| 1.1   | Product Overview                           |           |

| 1.2   | Product Configuration                      | 1-3       |

| Secti | on 2 Operation Outline                     | 2-1       |

| 2.1   | Screen Transitions                         | 2-2       |

| 2.2   | Setting Modulation Parameters              | 2-3       |

| 2.3   | Inputting Auxiliary Signal                 | 2-5       |

| 2.4   | Downloading Signal Pattern Files of MX3680 | 33A 2-5   |

| Secti | on 3 Details of Functions                  | 3-1       |

| 3.1   | 1xEV-DO Modulation Signal                  | 3-2       |

| 3.2   | Modulation Signal Details                  |           |

| 3.3   | External Trigger Input                     |           |

| 3.4   | Frame Trigger Output                       | 3-15      |

| Secti | on 4 Measurement                           | 4-1       |

| 4.1   | PER Measurement of AT Receiver             |           |

| 4.2   | PER Measurement of AN Receiver             | 4-3       |

| Secti | on 5 Remote Control                        |           |

| 5.1   | List of Device Messages Categorized by Fun | ction 5-2 |

5.2 Details of Device Messages in Alphabetical Order...... 5-4

| Section 6 Performance Test | 6-1 |

|----------------------------|-----|

|----------------------------|-----|

| 6.1 | Performance Test      | 6-2 |

|-----|-----------------------|-----|

| 6.2 | Output Level Accuracy | 6-4 |

| Appendix A | Specifications          | A-1    |

|------------|-------------------------|--------|

| Appendix B | List of Initial Value   | B-1    |

| Appendix C | Performance Test Record | C-1    |

| Index      | Ir                      | າdex-1 |

# Section 1 Overview

This section describes the outline and product configuration of MX368033A CDMA2000 1xEV-DO Signal Generation Software product and standard accessories.

| 1.1 | Product Overview      | 1-2 |

|-----|-----------------------|-----|

| 1.2 | Product Configuration | 1-3 |

### 1.1 Product Overview

The MX368033A CDMA2000 1xEV-DO Signal Generation Software (hereinafter, referred to as this software) is system software to be installed in the MU368030A Universal Modulation Unit.

To use this software, a Universal Modulation Unit must be mounted on the MG3681A Digital Modulation Signal Generator.

By installing this software, you can output modulation signals according to CDMA2000 1xEV-DO specifications, not using an external baseband signal source.

# **1.2 Product Configuration**

Standard configuration of the MX368033A is given in the table below. After unpacking, check that all items listed are included. If any items are missing or damaged, please contact Anritsu or one of our agencies.

| Items       | Model<br>name/type | Product name                                                              | Quan-<br>tity | Remarks                                           |

|-------------|--------------------|---------------------------------------------------------------------------|---------------|---------------------------------------------------|

| Main unit   | MX368033A          | CDMA2000 1xEV-DO<br>Signal Generation<br>Software                         | 1             | Supplied with Compact<br>Flash or ATA Flash card. |

|             |                    | PC card adapter                                                           | 1             | Supplied only with<br>Compact Flash card.         |

| Accessories |                    | CDMA2000 1xEV-DO<br>Signal Generation<br>Software Signal<br>Pattern Files | 1             | Supplied with CD-R.                               |

|             | M-W2072AE          | Operation Manual                                                          | 1             |                                                   |

Section 1 Overview

# Section 2 Operation Outline

This section describes basic screen contents and how to input auxiliary signals when mounting the MU368030A Universal Modulation Unit installed with this software onto the MG3681A.

| 2.1 | Screen Transitions                              | 2-2 |

|-----|-------------------------------------------------|-----|

| 2.2 | Setting Modulation Parameters                   | 2-3 |

| 2.3 | Inputting Auxiliary Signal                      | 2-5 |

|     | 2.3.1 Inputting external trigger signal         | 2-5 |

|     | 2.3.2 Inputting external reference clock signal | 2-5 |

| 2.4 | Downloading Signal Pattern Files of MX368033A   | 2-5 |

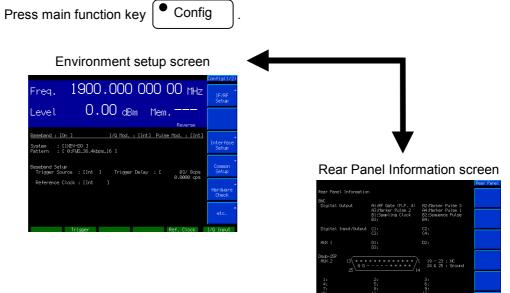

# 2.1 Screen Transitions

The screens are transited as shown below:

### 2.2 Setting Modulation Parameters

Pressing **•**Digital Mod causes the indicator LED to go on and the Main screen to appear. Basic parameters related to digital modulation can be set on this screen. This section describes settings for the Main screen.

[1] Baseband

Select On/Off for the operation of the Baseband Signal Generator Unit.

[2] I/Q Mod.

Select the I/Q signal source for orthogonal modulation. Select "Int" to use the internal signal source for the I/Q signal (using this software) or "Ext" to use the external input. Initial value: Int

[3] Pulse Mod.

Set the modulation signal on the pulse modulator.

- Int: Selects the control signal generated by this software.

- Ext: Uses the external input signal for pulse modulation regardless of modulation settings.

- Off: No pulse modulation

- [4] System

Set the system software. Select "1xEV-DO" to start this software.

[5] Pattern

Select the 1xEV-DO modulation signal. For selectable 1xEV-DO modulation signal, refer to "1xEV-DO modulation signal list" in Section 3.1.1.

| [6]  | Trigger Sourc                | e                                                                                                                                  |

|------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

|      | Switches the                 | inside and the outside of modulation signal transmit-                                                                              |

|      | ting timing.                 | For details, refer to Section 3.3.                                                                                                 |

|      | Int:                         | Outputs a RF signal in synchronization with a inter-<br>nal trigger signal.                                                        |

|      | Start:                       | Transmits a modulation signal using an external signal as the start signal.                                                        |

|      | Frame:                       | Transmits a modulation signal using an external sig-<br>nal as a frame trigger. (Not used in this software.)                       |

|      | Initial value:               | Int                                                                                                                                |

| [7]  | Trigger Delay                |                                                                                                                                    |

|      | TRIG connect                 | ut signal delay for the trigger signal input to the Start<br>or.<br>effer to Section 3.3.                                          |

|      |                              | : 0 to 16777215                                                                                                                    |

|      |                              | 0                                                                                                                                  |

| [8]  | Reference Clo                | ck                                                                                                                                 |

|      | Int: G                       | enerates the reference clock inside MG3681A.                                                                                       |

|      | С                            | hputs the reference clock from the outside. (The Ref.<br>clock connector is used.) In this case, set this connector<br>o TTL mode. |

|      |                              | ame as Ext (TTL) except that the Ref. Clock connector node should be set to AC (5 Vp-p).                                           |

| [9]  | Wave Data Re                 | estart                                                                                                                             |

|      |                              | button while Trigger Source is set to Start allows syn-<br>with the external trigger again.                                        |

| [10] | Wave Data Do                 | ownload                                                                                                                            |

|      | The 1xEV-DO refer to Section | modulation wave data can be re-installed. For details, on 2.4.                                                                     |

# 2.3 Inputting Auxiliary Signal

### 2.3.1 Inputting external trigger signal

You can synchronize the signal input at digital signal input connector No. 2,"Trigger," on the front panel of the MG3681A with the RF output timing. For details, refer to Section 3.3.

### 2.3.2 Inputting external reference clock signal

You can synchronize the signal input at digital signal input connector No. 5, "Ref. Clock," on the front panel of the MG3681A with the internal reference clock of the baseband signal. A 9830.4 kHz-signal that is 8 times of the chip rate (1228.8 ksps) can be input as the external reference clock. When using the 10/13 MHz Ref Input on the MG3681A main unit, both the RF and baseband signals are synchronized with the external input. However, when using this input, the RF signal remains to be synchronized with internal 10 MHz. The input frequency of external reference clock should be 9830.4 kHz  $\pm 5\%$ .

Relationship between the external reference clock settings and output signal reference clock is shown below.

| External Reference Clock Settings |                     | Output Signal Reference Clock |                            |  |

|-----------------------------------|---------------------|-------------------------------|----------------------------|--|

| Reference Clock                   | 10/13 MHz Ref Input | Baseband Signal               | RF Signal                  |  |

| Int                               | Int                 | Internal Reference            | Internal Reference         |  |

| Int                               | Ext                 | Ext 10/13 MHz Ref<br>Input    | Ext 10/13 MHz Ref<br>Input |  |

| Ext                               | Int                 | Ext Ref.Clock                 | Internal Reference         |  |

| Ext                               | Ext                 | Ext Ref.Clock                 | Ext 10/13 MHz Ref<br>Input |  |

# 2.4 Downloading Signal Pattern Files of MX368033A

It is available to download signal pattern files of 1xEV-DO modulation signal. First, insert the attached memory card, in which signal pattern files to be downloaded are saved, into the PC-card slot on the rear panel of the MG3681A. Then, press  $\boxed{F5}$  (Wave Data Download) in the Digital Modulation Parameter Setting Screen. Selecting "yes" in the Selecting window starts downloading. It takes approximately 12 minutes until completion. Do not cut power off while downloading is in progress.

# Section 3 Details of Functions

This section details the MX368033A CDMA2000 1xEV-DO Signal Generator Software functions.

| 3.1 | 1xEV-I | DO Modulation Signal                  | 3-2  |

|-----|--------|---------------------------------------|------|

|     | 3.1.1  | Overview of 1xEV-DO modulation signal | 3-2  |

| 3.2 | Modula | ation Signal Details                  | 3-5  |

|     | 3.2.1  | 1xEV-DO forward                       |      |

|     |        | (without FWD_Idle_Slot_MR)            | 3-5  |

|     | 3.2.2  | 1xEV-DO reverse                       | 3-10 |

|     | 3.2.3  | 1xEV-DO forward idle slot             | 3-13 |

| 3.3 | Extern | al Trigger Input                      | 3-14 |

| 3.4 | Frame  | Trigger Output                        | 3-15 |

# 3.1 1xEV-DO Modulation Signal

### 3.1.1 Overview of 1xEV-DO modulation signal

The 1xEV-DO modulation signal can be selected as a Pattern. The available 1xEV-DO modulation signals are shown below.

### FWD\_38.4\_16\_MR/.../FWD\_2457.6\_1\_MR

When those 1xEV-DO signals are selected, the CDMA2000 1xEV-DO forward modulation signal, where channel coding, TDM modulation and IQ mapping are conducted according to 3GPP2 C.S0024, is output.

### FWD\_Idle\_Slot\_MR

When this 1xEV-DO signal is selected, the CDMA2000 1xEV-DO forward idle slot modulation signal, where TDM modulation and IQ mapping are conducted according to 3GPP2 C.S0024, is output.

### RVS\_9.6 kbps/.../RVS\_153.6 kbps\_RT

When these 1xEV-DO signals are selected, the CDMA2000 1xEV-DO reverse modulation signal, where channel coding and IQ mapping are conducted according to 3GPP2 C.S0024, is output.

| No. | 1xEV-DO<br>Modulation Signal | Applicable System           | Baseband Filter | Data                   |

|-----|------------------------------|-----------------------------|-----------------|------------------------|

| 0   | FWD_38.4_16_MR               | CDMA2000 1xEV-DO<br>Forward | IS-95SPEC +EQ   | $\mathrm{PN15fix}^{*}$ |

| 1   | FWD_76.8_8_MR                | CDMA2000 1xEV-DO<br>Forward | IS-95SPEC +EQ   | $\mathrm{PN15fix}^{*}$ |

| 2   | FWD_153.6_4_MR               | CDMA2000 1xEV-DO<br>Forward | IS-95SPEC +EQ   | $\mathrm{PN15fix}^{*}$ |

| 3   | FWD_307.2_2_MR               | CDMA2000 1xEV-DO<br>Forward | IS-95SPEC +EQ   | $\mathrm{PN15fix}^{*}$ |

| 4   | FWD_614.4_1_MR               | CDMA2000 1xEV-DO<br>Forward | IS-95SPEC +EQ   | $\mathrm{PN15fix}^{*}$ |

| 5   | FWD_307.2_4_MR               | CDMA2000 1xEV-DO<br>Forward | IS-95SPEC +EQ   | $\mathrm{PN15fix}^{*}$ |

| 6   | FWD_614.4_2_MR               | CDMA2000 1xEV-DO<br>Forward | IS-95SPEC +EQ   | $\mathrm{PN15fix}^{*}$ |

| 7   | FWD_1228.8_1_MR              | CDMA2000 1xEV-DO<br>Forward | IS-95SPEC +EQ   | $\mathrm{PN15fix}^{*}$ |

| 8   | FWD_921.6_2_MR               | CDMA2000 1xEV-DO<br>Forward | IS-95SPEC +EQ   | $\mathrm{PN15fix}^{*}$ |

| 9   | FWD_1843.2_1_MR              | CDMA2000 1xEV-DO<br>Forward | IS-95SPEC +EQ   | $\mathrm{PN15fix}^{*}$ |

| 10  | FWD_1228.8_2_MR              | CDMA2000 1xEV-DO<br>Forward | IS-95SPEC +EQ   | $\mathrm{PN15fix}^{*}$ |

| 11  | FWD_2457.6_1_MR              | CDMA2000 1xEV-DO<br>Forward | IS-95SPEC +EQ   | $\mathrm{PN15fix}^{*}$ |

| 12  | FWD_Idle_Slot_MR             | CDMA2000 1xEV-DO<br>Forward | IS-95SPEC +EQ   | -                      |

| 13  | RVS_9.6 kbps                 | CDMA2000 1xEV-DO<br>Reverse | IS-95SPEC       | $PN9fix^*$             |

| 14  | RVS_19.2 kbps                | CDMA2000 1xEV-DO<br>Reverse | IS-95SPEC       | PN9fix <sup>*</sup>    |

| 15  | RVS_38.4 kbps                | CDMA2000 1xEV-DO<br>Reverse | IS-95SPEC       | PN9fix <sup>*</sup>    |

| 16  | RVS_76.8 kbps                | CDMA2000 1xEV-DO<br>Reverse | IS-95SPEC       | $PN9 fix^*$            |

| 17  | RVS_153.6 kbps               | CDMA2000 1xEV-DO<br>Reverse | IS-95SPEC       | $PN9 fix^*$            |

\*

Table 3-1

1xEV-DO Modulation Signal List

Data length is not an integer multiple of the PN sequence length (32767 bits for PN15 or 511 bits for PN9). The PN sequences are thus discontinuous at the data end.

### Section 3 Details of Functions

\*

| No. | 1xEV-DO<br>Modulation Signal | Applicable System           | Baseband Filter | Data        |  |  |  |

|-----|------------------------------|-----------------------------|-----------------|-------------|--|--|--|

| 19  | RVS_9.6 kbps_RT              | CDMA2000 1xEV-DO<br>Forward | IS-95SPEC       | $PN9fix^*$  |  |  |  |

| 20  | RVS_19.2 kbps_RT             | CDMA2000 1xEV-DO<br>Forward | IS-95SPEC       | $PN9fix^*$  |  |  |  |

| 21  | RVS_38.4 kbps_RT             | CDMA2000 1xEV-DO<br>Forward | IS-95SPEC       | $PN9fix^*$  |  |  |  |

| 22  | RVS_76.8 kbps_RT             | CDMA2000 1xEV-DO<br>Forward | IS-95SPEC       | $PN9fix^*$  |  |  |  |

| 23  | RVS_153.6 kbps_RT            | CDMA2000 1xEV-DO<br>Forward | IS-95SPEC       | $PN9 fix^*$ |  |  |  |

Table 3-1

1xEV-DO Modulation Signal List (Continuous)

Data length is not an integer multiple of the PN sequence length (32767 bits for PN15 or 511 bits for PN9). The PN sequences are thus discontinuous at the data end.

# 3.2 Modulation Signal Details

This section describes the 1xEV-DO forward, 1xEV-DO reverse and 1xEV-DO forward idle slot modulation signal configurations.

### 3.2.1 1xEV-DO forward (without FWD\_ldle\_Slot\_MR)

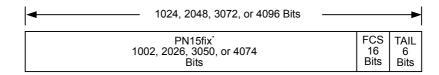

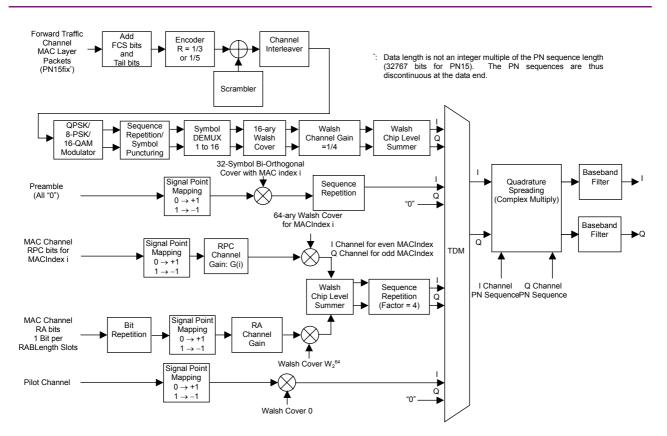

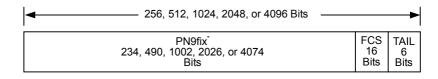

When a 1xEV-DO modulation signal from FWD\_38.4\_16\_MR to FWD\_2457.6\_1\_MR for Pattern is selected, the CDMA2000 1xEV-DO forward modulation signal where channel coding and IQ mapping are conducted according to 3GPP2 C.S0024, is output. The pilot, forward MAC and forward traffic channels are multiplexed on this output signal. For the forward traffic channel, PN15fix\* is used as the data before adding FCS (Frame check sequence.) The bit string format, after adding FCS and TAIL bit strings to the PN15fix bit string is shown in Figure 3-1. The bit string after adding FCS and TAIL bit strings to the PN15fix bit strings to the PN15fix bit string is called a packet in this manual.

Figure 3-1 Forward Packet Format

A packet goes through TDM (Time Division Multiplex) with other channels after channel coding including turbo-cording, scramble, channel interleaving and modulation (QPSK, 8-PSK, 16QAM), etc. The MACIndex used for scrambling is the same value as MACIndex used by the preamble in the same slot.

<sup>\*</sup> Data length is not the integer multiple of the PN sequence length (32767 bits for PN15). The PN sequences are thus discontinuous at the data end.

### Section 3 Details of Functions

Figure 3-2 1xEV-DO Forward Block Diagram

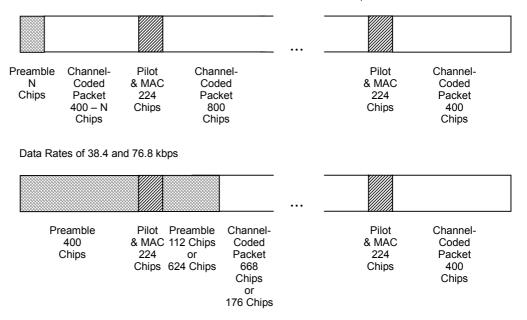

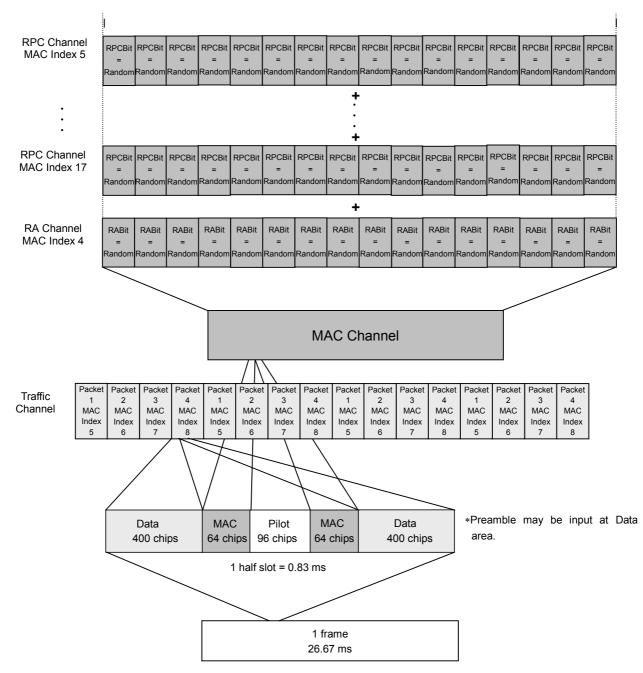

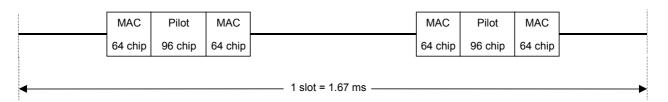

A packet after channel coding is then allocated to a data area in a slot together with a preamble with the same MACIndex during Time Division Multiplex. The slot format is shown in Figure 3-3. Time Division Multiplex status for preamble, packet after channel-coding, MAC channel and pilot channel are shown in Figure 3-4.

| Data      | MAC      | Pilot    | MAC      | Data             | MAC      | Pilot    | MAC      | Data      |

|-----------|----------|----------|----------|------------------|----------|----------|----------|-----------|

| 400 chips | 64 chips | 96 chips | 64 chips | 800 chips        | 64 chips | 96 chips | 64 chips | 400 chips |

|           |          |          |          |                  |          |          |          |           |

| •         |          |          |          | 1 slot = 1.67 ms |          |          |          |           |

Figure 3-3 Slot Format of 1xEV-DO Forward (without idle slot)

Data Rates of 153.6, 307.2, 614.4, 921.6, 1228.8, 1843.2 and 2457.6 kbps

Figure 3-4 Timing Diagram

4 PN15fix data with different initial values on the PN15 code generator as data for the forward traffic channel are created. Then a packet is created from each PN15fix data. Each packet goes through channel coding. The MACIndex values used by the scrambler differ according to each packet. (The same MACIndex as the packet is used for the preamble allocated to the slot together with that packet. For MACIndex values, refer to Figure 3-5.) A channel-coded packet is allocated to a slot in 3-slot intervals. Other packets that have gone through channel coding are allocated to the 3 intermediate slots. An example where forward traffic channels are allocated in 3-slot intervals is shown in Figure 3-5 while the forward traffic channel parameters are shown in Table 3-2.

### Section 3 Details of Functions

| No. | 1xEV-DO<br>Modulation Signal | Data Rate<br>(kbps) | Slot | Packet<br>(Bit) | Preamble<br>(Chip) | Modulation<br>Type |

|-----|------------------------------|---------------------|------|-----------------|--------------------|--------------------|

| 0   | FWD_38.4_16_MR               | 38.4                | 16   | 1024            | 1024               | QPSK               |

| 1   | FWD_76.8_8_MR                | 76.8                | 8    | 1024            | 512                | QPSK               |

| 2   | FWD_153.6_4_MR               | 153.6               | 4    | 1024            | 256                | QPSK               |

| 3   | FWD_307.2_2_MR               | 307.2               | 2    | 1024            | 128                | QPSK               |

| 4   | FWD_614.4_1_MR               | 614.4               | 1    | 1024            | 64                 | QPSK               |

| 5   | FWD_307.2_4_MR               | 307.2               | 4    | 2048            | 128                | QPSK               |

| 6   | FWD_614.4_2_MR               | 614.4               | 2    | 2048            | 64                 | QPSK               |

| 7   | FWD_1228.8_1_MR              | 1228.8              | 1    | 2048            | 64                 | QPSK               |

| 8   | FWD_921.6_2_MR               | 921.6               | 2    | 3072            | 64                 | 8-PSK              |

| 9   | FWD_1843.2_1_MR              | 1843.2              | 1    | 3072            | 64                 | 8-PSK              |

| 10  | FWD_1228.8_2_MR              | 1228.8              | 2    | 4096            | 64                 | 16QAM              |

| 11  | FWD_2457.6_1_MR              | 2457.6              | 1    | 4096            | 64                 | 16QAM              |

Table 3-2 Traffic Channel Parameters

MAC channel parameters are shown in Table 3-3.

Table 3-3 MAC Channel Parameters

| MACIndex                            | RABit  | RPCBit |

|-------------------------------------|--------|--------|

| 4(RA Channel),<br>5-17(RPC Channel) | Random | Random |

The RPCBit to be put on the RPC channel is arranged at random, while the RABit to be put on the RAChannel are at random. There are 13 RPC channels and one RA channel. Each MAC channel is spread by the Walsh Cover depending on MACIndex, and then multiplexed. A MAC channel is allocated to the MAC area in a slot as shown in Figure 3-3. The relationship between MAC channel, data sent from the traffic channel and slot is shown in Figure 3-5.

### 3.2 Modulation Signal Details

Figure 3-5 Multiplexing of each Channel

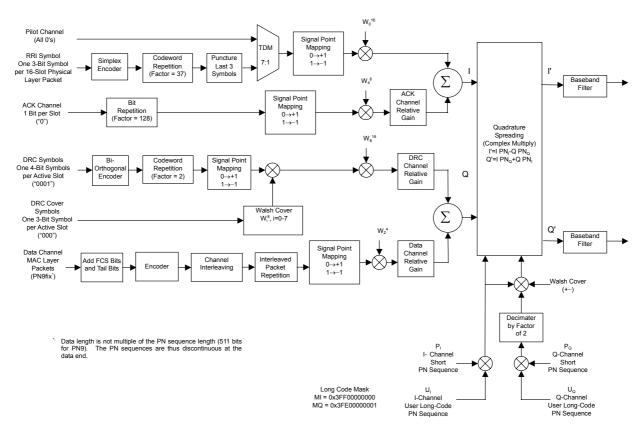

### 3.2.2 1xEV-DO reverse

When a 1xEV-DO modulation signal from RVS\_9.6 kbps to RVS\_153.6 kbps\_RT is selected for Pattern, the CDMA2000 1xEV-DO reverse modulation signal where channel coding and IQ mapping are conducted according to 3GPP2 C.S0024, is output. The pilot, RRI, DRC, ACK and data channels are multiplexed on this output signal. For the Data Channel, PN9fix\* is used as the data before FCS (Frame check sequence) is added. The bit string format after FCS and TAIL bit strings are added to the PN9fix bit string is shown in Figure 3-6.

Figure 3-6 Reverse Packet Format

The bit string after adding FCS and TAIL bit strings to the PN9fix bit string is multiplexed with the pilot, RRI, DRC and ACK channels after channel coding. The block diagram of 1xEV-DO is shown in Figure 3-7. Modulation parameters and channel gains for each are shown in Table 3-4 and 3-5, respectively.

Data length is not an integer multiple of the PN sequence length (511 bits). The PN sequences are thus discontinuous at the data end.

### 3.2 Modulation Signal Details

Figure 3-7 1xEV-DO Reverse – Block Diagram

| No. | 1xEV-DO<br>Modulation Signal | Data Rate<br>(kbps) | RRI<br>Symbol | DRC<br>Value | DRC<br>Cover | ACK<br>Channel Bit | Long Code<br>Mask |

|-----|------------------------------|---------------------|---------------|--------------|--------------|--------------------|-------------------|

| 13  | RVS_9.6 kbps                 | 9.6                 | 001           | 0x01         | $W_0^8$      | 0                  |                   |

| 14  | RVS_19.2 kbps                | 19.2                | 010           | 0x01         | $W_0^8$      | 0                  |                   |

| 15  | RVS_38.4 kbps                | 38.4                | 011           | 0x01         | $W_0^8$      | 0                  |                   |

| 16  | RVS_76.8 kbps                | 76.8                | 100           | 0x01         | $W_0^8$      | 0                  | MI =              |

| 17  | $RVS_{153.6 kbps}$           | 153.6               | 101           | 0x01         | $W_0^8$      | 0                  | 0x3FF00000000     |

| 19  | RVS_9.6 kbps_RT              | 9.6                 | 001           | 0x01         | $W_0^8$      | 0                  | MQ =              |

| 20  | RVS_19.2 kbps_RT             | 19.2                | 010           | 0x01         | $W_0^8$      | 0                  | 0x3FE00000001     |

| 21  | RVS_38.4 kbps_RT             | 38.4                | 011           | 0x01         | ${ m W_0}^8$ | 0                  |                   |

| 22  | $RVS_{76.8 kbps_{RT}}$       | 76.8                | 100           | 0x01         | $W_0^8$      | 0                  |                   |

| 23  | RVS_153.6 kbps_RT            | 153.6               | 101           | 0x01         | $W_0^8$      | 0                  |                   |

| Table 3-4 | <b>Reverse Modulation</b> | Parameters  |

|-----------|---------------------------|-------------|

|           |                           | i urumeters |

### Section 3 Details of Functions

| No. | 1xEV-DO<br>Modulation Signal | Data Rate<br>(kbps) | Data/ Pilot         | RRI/ Pilot | DRC/Pilot | ACK/Pilot |

|-----|------------------------------|---------------------|---------------------|------------|-----------|-----------|

| 13  | RVS_9.6 kbps                 | 9.6                 | $3.75~\mathrm{dB}$  | 0 dB       | 3.0 dB    | 3.0 dB    |

| 14  | RVS_19.2 kbps                | 19.2                | $6.75~\mathrm{dB}$  | 0 dB       | 3.0 dB    | 3.0 dB    |

| 15  | RVS_38.4 kbps                | 38.4                | $9.75~\mathrm{dB}$  | 0 dB       | 3.0 dB    | 3.0 dB    |

| 16  | $RVS_{76.8 kbps}$            | 76.8                | $13.25~\mathrm{dB}$ | 0 dB       | 3.0 dB    | 3.0 dB    |

| 17  | RVS_153.6 kbps               | 153.6               | $18.50~\mathrm{dB}$ | 0  dB      | 3.0 dB    | 3.0 dB    |

| 19  | RVS_9.6 kbps_RT              | 9.6                 | $3.75~\mathrm{dB}$  | 0 dB       | 3.0 dB    | 0 dB      |

| 20  | RVS_19.2 kbps_RT             | 19.2                | $6.75~\mathrm{dB}$  | 0 dB       | 3.0 dB    | 0 dB      |

| 21  | RVS_38.4 kbps_RT             | 38.4                | $9.75~\mathrm{dB}$  | 0 dB       | 3.0 dB    | 0 dB      |

| 22  | RVS_76.8 kbps_RT             | 76.8                | $13.25~\mathrm{dB}$ | 0 dB       | 3.0 dB    | 0 dB      |

| 23  | RVS_153.6 kbps_RT            | 153.6               | 18.50 dB            | 0 dB       | 3.0 dB    | 0 dB      |

Table 3-5 Reverse Channel Gain

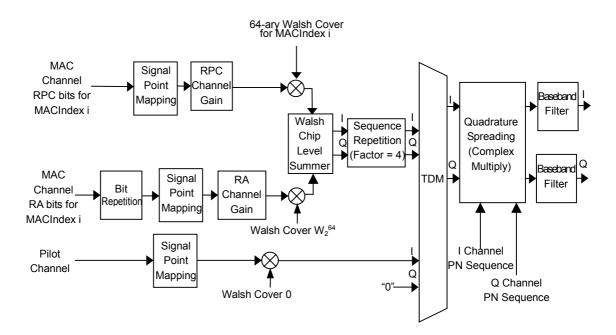

### 3.2.3 1xEV-DO forward idle slot

When FWD\_Idle\_Slot\_RT is selected for Pattern, the CDMA2000 1xEV-DO forward idle slot modulation signal where IQ mapping is conducted according to 3GPP2 C.S0024, is output. The pilot and forward, MAC channels are multiplexed on this output signal. RABit is "0" in all slots. The block diagram of the forward idle slot is shown below.

Figure 3-8 Forward Idle Slot – Block Diagram

The forward idle slot format is shown in Figure 3-9. MAC channel parameters for the forward idle slot are shown in Table 3-6.

Figure 3-9 1xEV-DO Forward Idle Slot Format

| MAC Index                             | RA Bit RPC Bit |        | RA Channel<br>Gain       | RPC Channel<br>Gain      |  |  |  |

|---------------------------------------|----------------|--------|--------------------------|--------------------------|--|--|--|

| 4 (RA Channel),<br>5-17 (RPC Channel) | Random         | Random | $-12.04~\mathrm{dB}^{*}$ | $-11.42~\mathrm{dB}^{*}$ |  |  |  |

Table 3-6 MAC Channel for Forward Idle Slot

Relative values for Pilot Channel

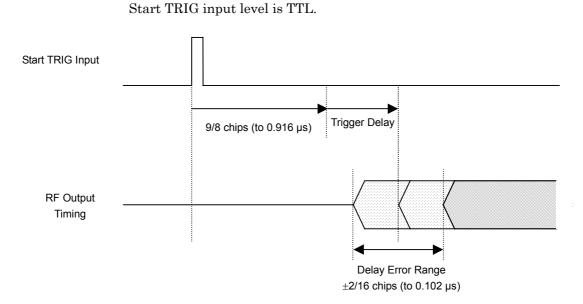

# 3.3 External Trigger Input

RF signal output timing for trigger signal inputs to the Start TRIG input (front panel) to synchronize with other devices is shown in the figure below. The RF signal is output with a delay of 9/8 chips (1 chip = 1/1228.8 ms) plus trigger delay set value from the trigger rise edge. The actual delay from Start TRIG input is as shown in the expression given below, as the RF output timing includes an error of  $\pm 2/16$  chips.

(Delay from Start TRIG input) =

9/8 chips + (Trigger Delay) ± (Delay error)

Figure 3-10 External Trigger Operation

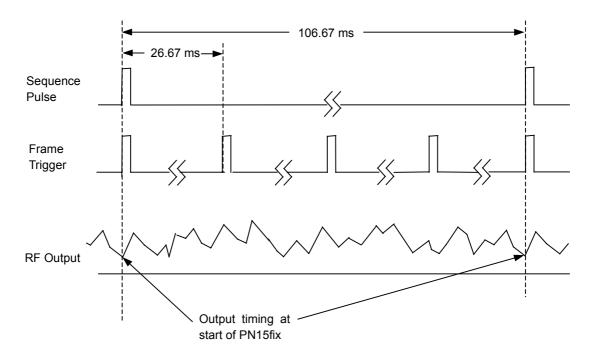

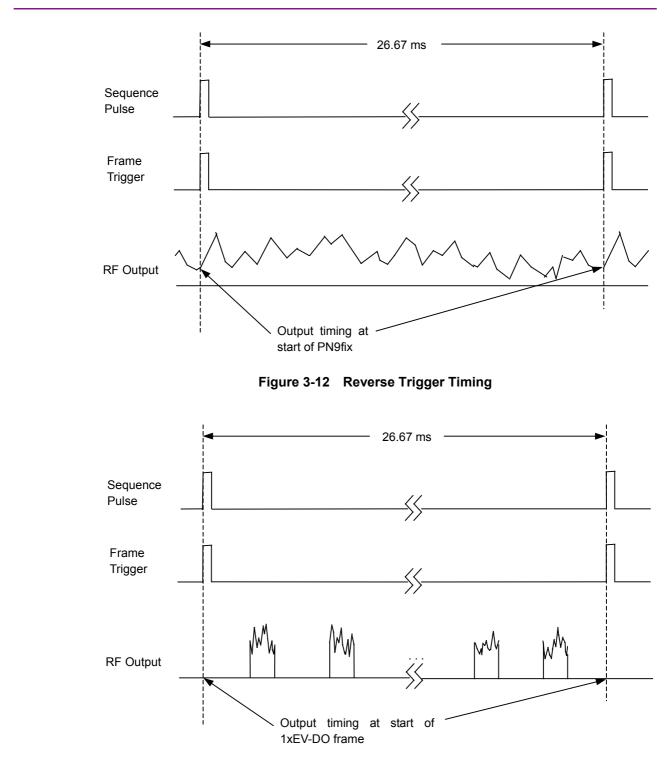

## 3.4 Frame Trigger Output

The Frame Trigger (A4) and Sequence Pulse (B2) are output from the BNC connector on the rear panel of the MG3681A. For the output timing of Frame Trigger, Sequence Pulse and RF output, refer to Figures 3-11 through 3-13.

Frame Trigger

The Frame Trigger is a TTL-level pulse signal synchronized with a 26.67ms 1xEV-DO frame. The pulse width is 1/8 chip. It is output from the A4 connector on the rear panel of the MG3681A.

#### Sequence Pulse

Sequence Pulse is a TTL-level pulse signal synchronized with the PN15fix repeat period when 1xEV-DO forward is selected for Pattern. It is synchronized with the PN9fix repeat period when 1xEV-DO reverse is selected, and it is synchronized with the 1xEV-DO frame when 1xEV-DO modulation signal FWD\_Idle\_Slot\_RT is selected. The pulse width is 1/8 chip. It is output from the B2 connector on the rear panel of the MG3681A.

Figure 3-11 Trigger Timing for Forward (excluding Idle Slot)

Section 3 Details of Functions

Figure 3-13 Trigger Timing for Forward Idle Slot

# Section 4 Measurement

This section explains each PER measurement of a Access Terminal (AT) receiver and Access Network (AN) receiver, as an example of measurement when mounting the MU368030A Universal Modulation Unit with MX368033A CDMA2000 1xEV-DO signal generation software onto the MG3681A Digital Modulation Signal Generator.

- 4.1 PER Measurement of AT Receiver ...... 4-2

- 4.2 PER Measurement of AN Receiver ...... 4-3

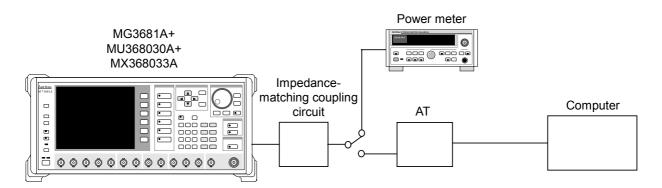

## 4.1 PER Measurement of AT Receiver

This section explains PER (Packet Error Rate) measurement of AT receiver. It explains as aim for receiver which enables setting of the receiving mode of traffic channel and reading of PER data with a computer, etc., without using the call processing.

Setup

Measuring procedures

- [1] Set the frequency and output level of the MG3681A to desired value.

- [2] Set the modulation system of the MG3681A to "1xEV-DO."

- [3] Set the measured 1xEV-DO modulation signal to Pattern of the MG3681A.

- [4] Connect RF output of the MG3681A to the power meter trough the impedance-matching coupling circuit. Then, adjust the output level of the MG3681A to obtain the sensitivity test level with the power meter.

- [5] Switch output of impedance-matching coupling circuit to the AT.

- [6] Set AT to the receiving mode using the computer.

- [7] Obtain the PER data from the AT using the computer.

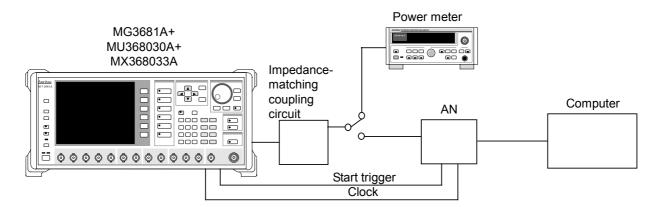

## 4.2 PER Measurement of AN Receiver

This section explains PER (Packet Error Rate) measurement of AN receiver. It explains as the object: the receiver which enables setting of the receiving mode of data channel and reading of PER data with a computer, etc., without using the call processing. In this case, it is needed that the start trigger synchronized with reference clock of 10 MHz or 9.8304 MHz, and 1xEV-DO frame, is output from AN.

#### Setup

#### Measuring procedures

- [1] Set the frequency and output level of the MG3681A to desired value.

- [2] Set the modulation system of the MG3681A to "1xEV-DO."

- [3] Set the measured 1xEV-DO modulation signal to Pattern of the MG3681A.

- [4] Connect the RF output of the MG3681A to the power meter through the impedance-matching coupling circuit. Then, adjust the output level of the MG3681A to obtain the sensitivity test level with the power meter.

- [5] Switch output of impedance-matching coupling circuit to the AN.

- [6] Synchronize the built-in Reference Clock of the MG3681A with the AN.

Set Trigger Source to "Start." As for Reference Clock, set "Ext" for use of Ref Clock and "Int" for use of 10/13MHz Ref Input respectively.

- [7] Set the receiver to the receiving mode using the computer.

- [8] Set Trigger Delay of the MG3681A to appropriate value.

- [9] Re-synchronize the MG3681A with the AN by pressing Wave Data Restart of the MG3681A.

- [10] Obtain PER data from the AN receiver using the computer.

# Section 5 Remote Control

This section provides a list of GPIB device messages categorized by function and also describes in detail these device messages arranged in alphabetical order, when the MU368030A Universal Modulation Unit installed with the MX368033A CDMA2000 1xEV-DO Signal Generation Software is mounted in the MG3681A Digital Modulation Signal Generator.

For further description of remote control, refer to Section 4 "Remote Control" in the MG3681A Main Unit Operation Manual.

- 5.1 List of Device Messages Categorized by Function ... 5-2

- 5.2 Details of Device Messages in Alphabetical Order.... 5-4

## 5.1 List of Device Messages Categorized by Function

#### Command and query messages

The header portion of the command message is a reserved word represented by capital alphanumeric characters. The end of a query message header contains an interrogation mark (?). In the argument part of command and query messages, multiple arguments can be separated with a separator (,). Arguments are described below.

| a se | eparator (,). Arguments               | are described below.                       |  |

|------|---------------------------------------|--------------------------------------------|--|

| [1]  | Capitals                              | : Reserved word                            |  |

| [2]  | Numerals                              | : Reserved word                            |  |

| [3]  | Small letters in argument part:       |                                            |  |

|      | f (Frequency)                         | : Numeric data (NR1, NR2, NR3)             |  |

|      | Suffix code                           | : GHZ, GZ, MHz, MZ, kHz, KZ, HZ            |  |

|      |                                       | When the unit is omitted, HZ is assumed.   |  |

|      |                                       |                                            |  |

|      | l (level) (relative value)            | : Numeric data (NR1, NR2, NR3 format)      |  |

|      | Suffix code                           | : dB                                       |  |

|      |                                       | When the unit is omitted, dB is assumed.   |  |

|      | n (integer without unit)              | : Numeric data (NR1 format)                |  |

|      | r (real number without unit) :        |                                            |  |

|      |                                       | Numeric data (NR2 format)                  |  |

|      | h (hexadecimal number without unit) : |                                            |  |

|      |                                       | Numeric data (hexadecimal number)          |  |

|      | s (character string)                  | : Alphanumeric characters enclosed in dou- |  |

|      |                                       | ble quotation marks (" ") or single quota- |  |

|      |                                       | tion marks (' ').                          |  |

|      |                                       |                                            |  |

|      |                                       |                                            |  |

#### Device messages list

#### <Common>

| Items               | Device messages  |                |                   |

|---------------------|------------------|----------------|-------------------|

| Control Items       | Command messages | Query messages | Response messages |

| I/Q Source Internal | MODE INT         | MODE?          | MODE INT          |

|                     | IQSRC INT        | IQSRC?         | IQSRC INT         |

| I/Q Source External | MODE EXT         | MODE?          | MODE EXT          |

|                     | IQSRC EXT        | IQSRC?         | IQSRC EXT         |

| I/Q Source OFF      | MODE OFF         | MODE?          | MODE OFF          |

|                     | IQSRC OFF        | IQSRC?         | IQSRC OFF         |

| System 1XEV-DO      | SYS 1XEV-DO      | SYS?           | SYS 1XEV-DO       |

| Baseband ON         | BASEBAND ON      | BASEBAND?      | BASEBAND ON       |

| Baseband OFF        | BASEBAND OFF     | BASEBAND?      | BASEBAND OFF      |

| PM ON               | PMO ON           | PMO?           | PMO ON            |

| PM OFF              | PMO OFF          | PMO?           | PMO OFF           |

#### <Modulation>

| Items                  | Device messages  |                |                   |

|------------------------|------------------|----------------|-------------------|

| Control Items          | Command messages | Query messages | Response messages |

| Wave Data Restart      | DLRES            | _              | _                 |

| Wave Data Download     | DOWNLOAD         | _              | _                 |

| Pattern                | PAT n            | PAT?           | PAT n,s           |

|                        | n: 0 to 23       |                |                   |

| Reference Clock Source | REFCLK INT       | REFCLK?        | REFCLK INT        |

| Reference Clock Source | REFCLK EXT       | REFCLK?        | REFCLK EXT        |

| Reference Clock Source | REFCLK EXT2      | REFCLK?        | REFCLK EXT2       |

| Start Trigger Delay    | STDLY n          | STDLY?         | STDLY n           |

|                        | n: 0 to 16777215 |                |                   |

| Start Trigger Source   | STGS INT         | STGS?          | STGS INT          |

| Start Trigger Source   | STGS EXT         | STGS?          | STGS EXT          |

| Start Trigger Source   | STGS EXTSTA      | STGS?          | STGS EXT          |

| Start Trigger Source   | STGS EXTFRM      | STGS?          | STGS EXTFRM       |

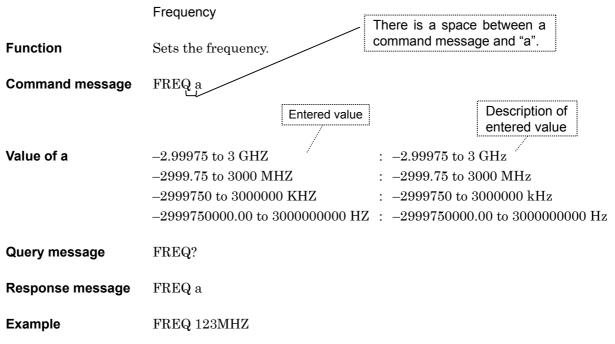

## 5.2 Details of Device Messages in Alphabetical Order

<Examples>

## FREQ

# BASEBAND

| Function         | Sets baseband On/Off.                  |

|------------------|----------------------------------------|

| Command message  | BASEBAND a                             |

| Value of a       | ON : Baseband On<br>OFF : Baseband Off |

| Query message    | BASEBAND?                              |

| Response message | BASEBAND a                             |

| Example          | BASEBAND ON                            |

Baseband (On/Off)

# DLRES

*D*\_\_\_\_

Wave Data Restart

| Function        | Re-synchronizes with the external trigger in the start trigger mode. |

|-----------------|----------------------------------------------------------------------|

| Command message | DLRES                                                                |

| Example         | DLRES                                                                |

## DOWNLOAD

Wave Data Download

Function

Downloads the modulation wave and switches the output modulation wave.

Command message DOWNLOAD

# IQSRC

|                  | I/Q Source                                                                                                                                                                |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Function         | Selects the modulation source for digital modulation.                                                                                                                     |  |

| Command message  | IQSRC a                                                                                                                                                                   |  |

| Value of a       | <ul> <li>INT : Internal (internal modulation unit)</li> <li>EXT : External (external input)</li> <li>OFF : I/Q modulation stop (only pulse modulation enabled)</li> </ul> |  |

| Query message    | IQSRC?                                                                                                                                                                    |  |

| Response message | IQSRC a                                                                                                                                                                   |  |

| Example          | IQSRC INT                                                                                                                                                                 |  |

I

# <u>Р</u> РАТ

|                  | Pattern                                                                                                                                                                                                                                   |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Function         | Selects the 1xEV-DO modulation signal.                                                                                                                                                                                                    |

| Command message  | PAT n                                                                                                                                                                                                                                     |

| Value of n       | 0 to 23                                                                                                                                                                                                                                   |

| Query message    | PAT?                                                                                                                                                                                                                                      |

| Response message | PAT n,s                                                                                                                                                                                                                                   |

| Restrictions     | "n" shows the1xEV-DO modulation signal number and "s" shows the name<br>of 1xEV-DO modulation signal. As for the1xEV-DO modulation signal<br>corresponding to "n" and "s", refer to "1xEV-DO Modulation Signal List" in<br>Section 3.1.1. |

| Example          | PAT 2                                                                                                                                                                                                                                     |

# PMO

|                  | Pulse-Modulation                                                                                                                                                |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Function         | Sets On/Off and Internal/External of pulse modulation.                                                                                                          |  |

| Command message  | PMO a                                                                                                                                                           |  |

| Value of a       | <ul><li>INT : Internal (generates with modulation unit)</li><li>EXT : External (uses external device signal)</li><li>OFF : Off (signals always exist)</li></ul> |  |

| Query message    | PMO?                                                                                                                                                            |  |

| Response message | PMO a                                                                                                                                                           |  |

| Example          | PMO INT                                                                                                                                                         |  |

# REFCLK

|                  | Reference Clock Source                                                                                                             |

|------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Function         | Selects the baseband reference timing (external or internal).                                                                      |

| Command message  | REFCLK a                                                                                                                           |

| Value of a       | <ul><li>INT : Internal selection</li><li>EXT : External (TTL) selection</li><li>EXT2 : External 2 (AC: 5 Vp-p) selection</li></ul> |

| Query message    | REFCLK?                                                                                                                            |

| Response message | REFCLK a                                                                                                                           |

| Example          | REFCLK INT                                                                                                                         |

# STDLY

|                  | Start Trigger delay amount        |

|------------------|-----------------------------------|

| Function         | Sets the RF signal output timing. |

| Command message  | STDLY n                           |

| Value of n       | 0 to 16777215                     |

| Query message    | STDLY?                            |

| Response message | STDLY n                           |

| Example          | STDLY 10                          |

# STGS

|                  | Start Trigger Source         |                                                                         |

|------------------|------------------------------|-------------------------------------------------------------------------|

| Function         | Sets Trigger Source.         |                                                                         |

| Command message  | STGS a                       |                                                                         |

| Value of a       | INT<br>EXTSTA, EXT<br>EXTFRM | : Internal trigger mode<br>: Start trigger mode<br>: Frame trigger mode |

| Query message    | STGS?                        |                                                                         |

| Response message | STGS a                       |                                                                         |

| Example          | STGS INT                     |                                                                         |

$\underline{S}$

# SYS

|                  | System                                                                                           |  |

|------------------|--------------------------------------------------------------------------------------------------|--|

| Function         | Sets the digital modulation system.                                                              |  |

| Command message  | SYS a                                                                                            |  |

| Value of a       | NONE: Digital modulation system not mounted.1XEV-DO: CDMA2000 1xEV-DO Signal Generation Software |  |

| Query message    | SYS?                                                                                             |  |

| Response message | SYS a                                                                                            |  |

| Example          | SYS 1XEV-DO                                                                                      |  |

# Section 6 Performance Test

This section describes the performance test when MX368033A CDMA2000 1xEV-DO Signal Generation Software is installed on the MU368030A Universal Modulation Unit, which is mounted on the MG3681A Digital Modulation Signal Generator. In order to implement the performance test as preventive maintenance, information such as required measuring instrument, setup procedure, and test procedures are included.

| 6.1 | 1 Performance Test |                            |     |  |

|-----|--------------------|----------------------------|-----|--|

|     | 6.1.1              | About the performance test | 6-2 |  |

|     | 6.1.2              | Instruments required for   |     |  |

|     |                    | the performance test       | 6-3 |  |

| 6.2 | Output             | Level Accuracy             | 6-4 |  |

|     |                    |                            |     |  |

## 6.1 Performance Test

#### 6.1.1 About the performance test

The performance test explained here is implemented as part of preventive maintenance against performance deterioration of the instrument. You are advised to implement a performance test whenever necessary, for examples, upon acceptance inspection, regular inspection, and post-repair performance confirmation. If you find an item, which does not meet specifications during a performance test, please contact Anritsu Corporation or one of our dealers.

The performance test consists of the following items:

• Output level accuracy

Be sure to implement periodically the performance test for items considered important as preventive maintenance. We recommend that the performance inspection is executed regularly once or twice a year.

In addition, it is recommended that the results are summarized using the Appendix C "Performance Test Record."

## CAUTION A

Unless otherwise specified, be sure to warm up the device to be tested and the measuring instruments for at least 30 minutes or over until they become stable, before implementing the performance test. To ensure the maximum measurement accuracy, we recommend that you observe the above as well as keeping the room temperature, limiting AC power voltage fluctuations to a minimum, and making sure that there are no problems with noise, vibration, dust, humidity or other environmental factors.

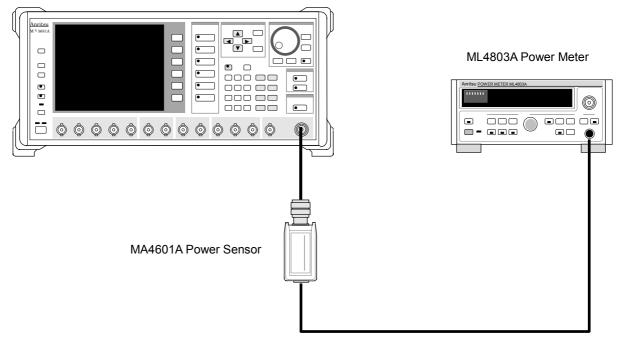

## 6.1.2 Instruments required for the performance test

A list of instruments required for the performance test is shown below.

| Test Item             | Recommended Instrument | Anritsu Model Name |  |

|-----------------------|------------------------|--------------------|--|

| Output level accuracy | Power meter            | ML4803A            |  |

|                       | Power sensor           | MA4601A            |  |

# 6.2 Output Level Accuracy

Test specifications

Difference from output level at CW±1.5 dBConditionsRF output level≤-3 dBmCarrier frequency10 to 3000 MHzLevel continuous modeOff

Test procedure

#### MG3681A

+ MU368030A (Universal Modulation Unit)

+ MX368033A (CDMA2000 1xEV-DO Signal Generation Software)

[1] Set the modulation parameter of MG3681A as shown below:

| Preset                    | :—                                   |

|---------------------------|--------------------------------------|

| Baseband                  | : On                                 |

| I/Q Mod                   | : Int                                |

| <b>Digital Modulation</b> | : On                                 |

| System                    | : 1XEV-DO                            |

| Pattern                   | : Measured 1xEV-DO modulation signal |

- [2] Set RF Output of MG3681A to Off.

- [3] Perform adjustment of zero point and calibrate sensor sensitivity of Power meter.

- [4] Set the output level of MG3681A to measured value. (In the above system, the measurement-enabled minimum level depends on the sensitivity of power sensor.)

- [5] Set the calibration coefficient of sensor in the power meter.

- [6] Set the Digital Modulation of the MG3681A to Off, and measure the output level of the MG3681A at CW.

- [7] Set the Digital Modulation to On, and measure the output level of the MG3681A in modulating.

- [8] Confirm that difference between the output level at CW and the output level in modulating is within specification.

# Appendix

| Appendix A | Specifications          | A-1 |

|------------|-------------------------|-----|

| Appendix B | List of Initial Value   | B-1 |

| Appendix C | Performance Test Record | C-1 |

Appendix

# Appendix A Specifications

| ltem                                         |                                   |                                                           | Specifications                                                                                                                                                                             |

|----------------------------------------------|-----------------------------------|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Corresponding<br>system/Modulation<br>system |                                   | Forward channel :<br>Reverse channel :                    | Corresponding specifications 3GPP2 C.S0024<br>16QAM, 8PSK, QPSK (Data), QPSK (Spreading)<br>BPSK (Data), HPSK (Spreading)                                                                  |

| Baseban                                      | d Filter                          |                                                           | FIR filter according to IS-95<br>FIR filter with equalizer according to IS-95                                                                                                              |

| Modulation data                              | Forward<br>common                 | Channel configuration<br>Pilot channel<br>Traffic channel | <ul> <li>Pilot channel, Traffic channel,<br/>Time division multiplex of MAC channel</li> <li>All 0, Walsh cover=0</li> <li>Packet data PN15fix<br/>(4 Frame, without Idle slot)</li> </ul> |

| Mo                                           |                                   | MAC channel<br>RPC bit of RPC channel                     | : Head slot of frame is All "1", the others are All "0".<br>Channel power=–11.46 dB                                                                                                        |

|                                              |                                   | RA bit of RA channel<br>Or, the following MAC cha         | : All 0, Channel power=–11.46 dB<br>annel                                                                                                                                                  |

|                                              |                                   | RPC bit of RPC channel<br>RA bit of RA channel            | : Random, channel power=–12.04 dB<br>: Random, channel power=–11.42 dB                                                                                                                     |

|                                              | Forward<br>38.4 kbps,<br>16 slots | Preamble<br>MAC Index<br>Traffic channel                  | <ul> <li>: 1024-bit</li> <li>: 4 (RA channel), 5 to 17 (RPC channel)</li> <li>: QPSK modulation, Data rate=38.4 kbps,<br/>Number of time division multiplex 16 slots</li> </ul>            |

|                                              | Forward<br>76.8 kbps,<br>8 slots  | Preamble<br>MAC Index<br>Traffic channel                  | <ul> <li>: 512-bit</li> <li>: 4 (RA channel), 5 to 17 (RPC channel)</li> <li>: QPSK modulation, Data rate=76.8 kbps,<br/>Number of time division multiplex 8 slots</li> </ul>              |

|                                              | Forward<br>153.6 kbps,<br>4 slots | Preamble<br>MAC Index<br>Traffic channel                  | <ul> <li>: 256-bit</li> <li>: 4 (RA channel), 5 to 17 (RPC channel)</li> <li>: QPSK modulation, Data rate=153.6 kbps,<br/>Number of time division multiplex 4 slots</li> </ul>             |

|                                              | Forward<br>307.2 kbps,<br>2 slots | Preamble<br>MAC Index<br>Traffic channel                  | <ul> <li>: 128-bit</li> <li>: 4 (RA channel), 5 to 17 (RPC channel)</li> <li>: QPSK modulation, Data rate=307.2 kbps,<br/>Number of time division multiplex 2 slots</li> </ul>             |

|                                              | Forward<br>614.4 kbps,<br>1 slot  | Preamble<br>MAC Index<br>Traffic channel                  | <ul> <li>: 64-bit</li> <li>: 4 (RA channel), 5 to 17 (RPC channel)</li> <li>: QPSK modulation, Data rate=614.4 kbps,<br/>Number of time division multiplex 1 slot</li> </ul>               |

#### When installed in MU368030A mounted on MG3681A

#### Note:

Channel power is the value where the pilot channel power is set to 0 dB.

#### Appendix A Specifications

|                 | ltem                               |                                          | Specifications                                                                                                                                                                  |

|-----------------|------------------------------------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Modulation data | Forward<br>307.2 kbps,<br>4 slots  | Preamble<br>MAC Index<br>Traffic channel | <ul> <li>: 128-bit</li> <li>: 4 (RA channel), 5 to 17 (RPC channel)</li> <li>: QPSK modulation, Data rate=307.2 kbps,<br/>Number of time division multiplex 4 slots</li> </ul>  |

|                 | Forward<br>614.4 kbps,<br>2 slots  | Preamble<br>MAC Index<br>Traffic channel | : 64-bit<br>: 4 (RA channel), 5 to 17 (RPC channel)<br>: QPSK modulation, Data rate=614.4 kbps,<br>Number of time division multiplex 2 slots                                    |

|                 | Forward<br>1228.8 kbps,<br>1 slot  | Preamble<br>MAC Index<br>Traffic channel | : 64-bit<br>: 4 (RA channel), 5 to 17 (RPC channel)<br>: QPSK modulation, Data rate=1228.8 kbps,<br>Number of time division multiplex 1 slot                                    |

|                 | Forward<br>921.6 kbps,<br>2 slots  | Preamble<br>MAC Index<br>Traffic channel | <ul> <li>: 64-bit</li> <li>: 4 (RA channel), 5 to 17 (RPC channel)</li> <li>: 8PSK modulation, Data rate=921.6 kbps,<br/>Number of time division multiplex 2 slots</li> </ul>   |

|                 | Forward<br>1843.2 kbps,<br>1 slot  | Preamble<br>MAC Index<br>Traffic channel | : 64-bit<br>: 4 (RA channel), 5 to 17 (RPC channel)<br>: 8PSK modulation, Data rate=1843.2 kbps,<br>Number of time division multiplex 1 slots                                   |

|                 | Forward<br>1228.8 kbps,<br>2 slots | Preamble<br>MAC Index<br>Traffic channel | <ul> <li>: 64-bit</li> <li>: 4 (RA channel), 5 to 17 (RPC channel)</li> <li>: 16QAM modulation, Data rate=1228.8 kbps,<br/>Number of time division multiplex 2 slots</li> </ul> |

|                 | Forward<br>2457.6 kbps,<br>1 slot  | Preamble<br>MAC Index<br>Traffic channel | : 64-bit<br>: 4 (RA channel), 5 to 17 (RPC channel)<br>: 16QAM modulation, Data rate=2457.6 kbps,<br>Number of time division multiplex 1 slot                                   |

|                 | Forward<br>Idle slot               | MAC Index                                | : 4 (RA channel), 5 to 17 (RPC channel)                                                                                                                                         |

|                 | ltem                     |                                              | Specifications                                                                                                |

|-----------------|--------------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| Modulation data | Reverse<br>common        | DRC channel<br>RRI channel<br>Long code mask | : "0001", DRC cover symbol "0", Channel power=3.0 dB<br>: Channel power=0.0 dB<br>: MI=3FF00000000 (16 Hex.), |

| odula           |                          | Data channel                                 | MQ=3FE00000001 (16 Hex.)<br>: PN9fix data (1 frame length)                                                    |

| M               | Reverse<br>9.6 kbps      | Data channel<br>RRI symblol<br>ACK channel   | : Data rate=9.6 kbps, Channel power=3.75 dB<br>: "001"<br>: All 0, Channel power=3.0 dB                       |

|                 | Reverse<br>19.2 kbps     | Data channel<br>RRI symbol<br>ACK channel    | : Data rate=19.2 kbps, Channel power=6.75 dB<br>: "010"<br>: All 0, Channel power=3.0 dB                      |

|                 | Reverse<br>38.4 kbps     | Data channel<br>RRI symbol<br>ACK channel    | : Data rate=38.4 kbps, Channel power=9.75 dB<br>: "011"<br>: All 0, Channel power=3.0 dB                      |

|                 | Reverse<br>76.8 kbps     | Data channel<br>RRI symbol<br>ACK channel    | : Data rate=76.8 kbps, Channel power=13.25 dB<br>: "100"<br>: All 0, Channel power=3.0 dB                     |

|                 | Reverse<br>153.6 kbps    | Data channel<br>RRI symbol<br>ACK channel    | : Data rate=153.6 kbps, Channel power=18.50 dB<br>: "101"<br>: All 0, Channel power=3.0 dB                    |

|                 | Reverse<br>9.6 kbps_RT   | Data channel<br>RRI symbol<br>ACK channel    | : Data rate=9.6 kbps, Channel power=3.75 dB<br>: "001"<br>: All 0, Channel power=0.0 dB                       |

|                 | Reverse<br>19.2 kbps_RT  | Data channel<br>RRI symbol<br>ACK channel    | : Data rate=19.2 kbps, Channel power=6.75 dB<br>: "010"<br>: All 0, Channel power=0.0 dB                      |

|                 | Reverse<br>38.4 kbps_RT  | Data channel<br>RRI symbol<br>ACK channel    | : Data rate=38.4 kbps, Channel power=9.75 dB<br>: "011"<br>: All 0, Channel power=0.0 dB                      |

|                 | Reverse<br>76.8 kbps_RT  | Data channel                                 | : Data rate=76.8 kbps, Channel power=13.25 dB<br>: "100"<br>: All 0, Channel power=0.0 dB                     |

|                 | Reverse<br>153.6 kbps_RT | Data channel                                 | : Data rate=153.6 kbps, Channel power=18.50 dB<br>: "101"<br>: All 0, Channel power=0.0 dB                    |

#### Note:

Channel power is the value where the pilot channel power is set to 0 dB.

#### Appendix A Specifications

| ltem         |                      | Specifications                                                       |                                                       |  |  |  |

|--------------|----------------------|----------------------------------------------------------------------|-------------------------------------------------------|--|--|--|

| RF<br>signal | Frequency range      | 10 to 3000 MHz                                                       |                                                       |  |  |  |

|              | Level range          | -143 to 5 dBm                                                        |                                                       |  |  |  |

|              | Level<br>accuracy    | $\pm 1.5$ dB or less ( $\leq -3$ dBm) for output level as against CW |                                                       |  |  |  |

|              | Spurious<br>emission | In the range from 100 to 230<br>power in 30 kHz bandwidth            | 0 MHz, ratio of all power at -3 dBm output to         |  |  |  |

|              |                      | (PLL mode: Normal)                                                   |                                                       |  |  |  |

|              |                      | ≤–65 dBc (885 kHz to 1.98 MI<br>≤–77 dBc (2.5 to 5.0 MHz offs        | Hz offset), ≤–70 dBc (1.98 to 2.5 MHz offset),<br>et) |  |  |  |

|              |                      | (Note: Performance degrada excluded.)                                | tion caused by Spurious from MG3681A is               |  |  |  |

| IQ           | Output               | Forward 38.4 kbps 16 slots                                           | : 149 mV (rms)                                        |  |  |  |

| signal       | level                | Forward 76.8 kbps 8 slots                                            | : 149 mV (rms)                                        |  |  |  |

|              |                      | Forward 153.6 kbps 4 slots                                           | : 149 mV (rms)                                        |  |  |  |

|              |                      | Forward 307.2 kbps 2 slots                                           | : 149 mV (rms)                                        |  |  |  |

|              |                      | Forward 614.4 kbps 1 slot                                            | : 149 mV (rms)                                        |  |  |  |

|              |                      | Forward 307.2 kbps 4 slots                                           | : 149 mV (rms)                                        |  |  |  |

|              |                      | Forward 614.4 kbps 2 slots                                           | : 149 mV (rms)                                        |  |  |  |

|              |                      | Forward 1228.8 kbps 1 slot                                           | : 149 mV (rms)                                        |  |  |  |

|              |                      | Forward 921.6 kbps 2 slots                                           | : 149 mV (rms)                                        |  |  |  |

|              |                      | Forward 1843.2 kbps 1 slot                                           | : 149 mV (rms)                                        |  |  |  |

|              |                      | Forward 1228.8 kbps 2 slots                                          | : 149 mV (rms)                                        |  |  |  |

|              |                      | Forward 2457.6 kbps 1 slot                                           | : 149 mV (rms)                                        |  |  |  |

|              |                      | Forward idle slot                                                    | : 149 mV (rms)                                        |  |  |  |

|              |                      | Reverse 9.6 kbps                                                     | : 252 mV (rms)                                        |  |  |  |

|              |                      | Reverse 19.2 kbps                                                    | : 254 mV (rms)                                        |  |  |  |

|              |                      | Reverse 38.4 kbps                                                    | : 269 mV (rms)                                        |  |  |  |

|              |                      | Reverse 76.8 kbps                                                    | : 199 mV (rms)                                        |  |  |  |

|              |                      | Reverse 153.6 kbps                                                   | : 301 mV (rms)                                        |  |  |  |

|              |                      | Reverse 9.6 kbps_RT                                                  | : 252 mV (rms)                                        |  |  |  |

|              |                      | Reverse 19.2 kbps_RT                                                 | : 254 mV (rms)                                        |  |  |  |

|              |                      | Reverse 38.4 kbps_RT                                                 | : 269 mV (rms)                                        |  |  |  |

|              |                      | Reverse 76.8 kbps_RT                                                 | : 199 mV (rms)                                        |  |  |  |

|              |                      | Reverse 153.6 kbps_RT                                                | : 301 mV (rms)                                        |  |  |  |

| Item                      |          | Specifications                                                                       |

|---------------------------|----------|--------------------------------------------------------------------------------------|

| mission Transmission Depe |          | 1.2288 Mcps                                                                          |